基于中档FPGA实现高速DDR3存储器控制器 数据处理与存储支持服务的设计与实现

随着数据密集型应用如高清视频处理、实时信号分析和高速网络通信的飞速发展,对存储系统的带宽和延迟提出了更高要求。DDR3 SDRAM因其高带宽、大容量和相对成熟的生态系统,仍是许多嵌入式系统的核心存储选择。直接使用DDR3的复杂性很高,需要一个高效的存储器控制器作为处理器或逻辑单元与物理存储颗粒之间的桥梁。利用中档现场可编程门阵列(FPGA)实现高速DDR3控制器,成为一种极具成本效益和灵活性的解决方案,能够为上层应用提供强大的数据处理与存储支持服务。

一、中档FPGA的优势与挑战

中档FPGA(如Xilinx Artix-7/Kintex-7系列、Intel Cyclone V/10系列)提供了足够的逻辑资源、存储块和高速I/O引脚,同时保持了合理的功耗和成本。其核心优势在于可编程性,允许设计者定制控制器的微架构,以精确匹配特定应用的数据访问模式(如顺序流、随机访问或突发访问)。挑战也同样存在:DDR3接口的物理层(PHY)和存储器控制器(MC)设计复杂,涉及精确的时序约束、信号完整性问题以及繁重的验证工作。幸运的是,主流FPGA厂商通常提供经过硅验证的DDR3 IP核(如Xilinx MIG或Intel UniPHY),大幅降低了底层实现的难度,使开发者能够聚焦于控制器逻辑与数据处理服务的构建。

二、DDR3控制器核心架构设计

一个完整的DDR3存储器控制器系统通常包含以下几个关键模块:

- 用户接口层:提供简洁的读写命令接口(如AXI4或自定义流接口),将上层应用逻辑的请求转换为控制器能理解的指令。设计时需考虑命令队列深度、仲裁策略(如轮询、优先级)以优化吞吐量和公平性。

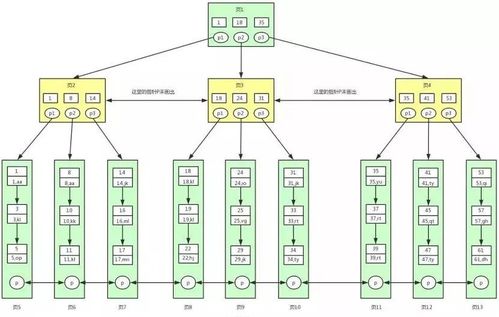

- 命令调度与地址映射模块:这是控制器的“大脑”。它负责将逻辑地址转换为DDR3的物理地址(行、列、Bank),并优化命令调度以最大化总线利用率。关键技术包括:

- Bank交错访问:通过合理安排对不同Bank的操作,隐藏行激活(ACT)和预充电(PRE)的时间,提高并发性。

- 命令重新排序:在遵守DDR3时序规则(如tRC、tFAW)的前提下,对读写命令进行智能排序,减少总线空闲时间。

- 地址映射策略:根据应用的数据布局(如帧缓存、矩阵存储),优化映射方式以减少行冲突。

- PHY接口层:负责与FPGA内置的DDR3 PHY IP进行对接,生成精确的时钟、地址、命令和数据信号。这一层需要严格满足由IP核提供的时序约束,确保在高速(如800MHz或1066MHz数据率)下的稳定运行。

- 数据通路与缓存:为了匹配用户逻辑与DDR3之间的速度差异,通常需要数据缓冲(FIFO或Buffer)。写数据路径可能包含写数据FIFO和可选的纠错码(ECC)生成逻辑;读数据路径则包含读数据FIFO、ECC校验和数据对齐电路。

三、数据处理与存储支持服务的实现

基于上述控制器核心,可以构建面向应用的数据处理与存储支持服务,这是体现FPGA方案价值的关键。

- 高性能直接内存访问(DMA)引擎:在FPGA内集成自定义DMA控制器,能够在不占用主处理器资源的情况下,实现数据在DDR3与外设(如ADC、网络MAC、视频接口)之间的高速搬移。DMA引擎可以支持描述符链表、分散-聚集(Scatter-Gather)操作,复杂的数据打包/解包格式,极大提升系统效率。

- 智能数据预取与缓存:针对图像处理、科学计算等具有空间或时间局部性的访问模式,可以在控制器前端实现预取器。通过分析访问地址流,预测并提前将数据从DDR3读入FPGA内部的Block RAM缓存,从而隐藏访存延迟,提升处理单元的运算效率。

- 实时数据重组与格式转换:FPGA的并行处理能力使其擅长进行流式数据操作。控制器可以集成数据宽度转换(如64位DDR接口到128位处理单元)、字节序交换、像素格式转换(如RGB到YUV)等功能,使得数据在存入或取出DDR3的同时即完成预处理,减少后续处理环节的负担。

- 可靠性与纠错服务:利用DDR3的ECC功能或自定义的更强纠错编码(如CRC),为关键数据提供检错和纠错能力,增强系统在恶劣环境下的可靠性。控制器可以透明地管理ECC数据的存储与校验。

- 多端口访问与虚拟化服务:通过时分复用或真正的多端口缓冲设计,一个物理DDR3控制器可以为FPGA内部的多个主设备(如多个处理器核、多个硬件加速器)提供并发的、受仲裁的存储访问服务,实现存储资源的虚拟化和高效共享。

四、设计验证与性能优化

实现一个稳定高效的控制器离不开 rigorous 的验证和优化。

- 仿真验证:使用厂商提供的DDR3仿真模型,在RTL级进行全面的功能仿真,覆盖各种边界情况和时序场景。

- 静态时序分析(STA):确保所有路径满足FPGA内部和DDR3接口的建立/保持时间要求。

- 板上测试与眼图分析:利用逻辑分析仪和示波器(或FPGA内置的IBERT等工具)测试实际信号完整性,调整I/O驱动强度和均衡设置,确保在目标频率下拥有良好的信号“眼图”。

- 性能剖析与调优:通过内置的性能计数器监控带宽利用率、平均延迟、Bank冲突率等指标,持续调整调度算法和缓存策略,直至满足应用需求。

五、应用场景与

基于中档FPGA的DDR3控制器及其数据处理服务,已广泛应用于软件定义无线电(SDR)中的大数据缓冲、工业相机中的帧缓存与预处理、金融技术中的低延迟交易系统以及嵌入式人工智能中的权重与特征图存储。它提供了一个在性能、成本、功耗和灵活性之间取得优异平衡的存储解决方案。

利用中档FPGA实现高速DDR3存储器控制器,远不止是提供一个简单的存储接口。通过精心设计控制器架构并集成智能的数据处理服务,开发者能够释放DDR3的全部带宽潜力,为上层应用构建一个高效、可靠、可定制的数据存储与处理基石,从而在激烈的技术竞争中赢得关键优势。

如若转载,请注明出处:http://www.mitaodiary.com/product/54.html

更新时间:2026-04-16 16:14:34